# Effects of active layer thickness on performance and stability of dual-active-layer amorphous InGaZnO thin film transistors\*

Wenxing Huo(霍文星)<sup>1,2</sup>, Zengxia Mei(梅增霞)<sup>1,†</sup>, Yicheng Lu(卢毅成)<sup>3</sup>, Zuyin Han(韩祖银)<sup>1,2</sup>, Rui Zhu(朱锐)<sup>1,2</sup>, Tao Wang(王涛)<sup>1,2</sup>, Yanxin Sui(隋妍心)<sup>1,2</sup>, Huili Liang(梁会力)<sup>1</sup>, and Xiaolong Du(杜小龙)<sup>1,4,‡</sup>

<sup>1</sup>Key Laboratory for Renewable Energy, Beijing Key Laboratory for New Energy Materials and Devices, Institute of Physics, Chinese Academy of Sciences, Beijing 100190, China

<sup>2</sup>School of Physical Sciences, University of Chinese Academy of Sciences, Beijing 100049, China

<sup>3</sup>Department of Electrical and Computer Engineering, Rutgers University, 94 Brett Rd, Piscataway, New Jersey 08854

<sup>4</sup> Songshan Lake Materials Laboratory, Dongguan 523808, China

(Received 3 April 2019; revised manuscript received 4 June 2019; published online 9 July 2019)

Dual-active-layer (DAL) amorphous InGaZnO (IGZO) thin film transistors (TFTs) are fabricated at low temperature without post-annealing. A bottom low-resistance (low-*R*) IGZO layer and a top high-resistance (high-*R*) IGZO layer constitute the DAL homojunction with smooth and high-quality interface by *in-situ* modulation of oxygen composition. The performance of DAL TFT is significantly improved when compared to that of single-active-layer. A detailed investigation was carried out regarding the effects of the thickness of both layers on the electrical properties and gate bias stress stabilities. It is found that the low-*R* layer improves the mobility, ON/OFF ratio, threshold voltage and hysteresis voltage by passivating the defects and providing smooth interface. The high-*R* IGZO layer has a great impact on the hysteresis, which changes from clockwise to counterclockwise. The best TFT shows a mobility of  $5.41 \text{ cm}^2/\text{V} \cdot \text{s}$ , a sub-threshold swing of 95.0 mV/dec, an ON/OFF ratio of  $6.70 \times 10^7$ , a threshold voltage of 0.24 V, and a hysteresis voltage of 0.13 V. The value of threshold voltage shifts under positive gate bias stress decreases when increasing the thickness of both layers.

Keywords: thin film transistor (TFT), InGaZnO, dual-active-layer

PACS: 73.61.Ga, 77.55.hf, 85.30.-z, 85.30.Tv

## 1. Introduction

Amorphous oxide semiconductors (AOSs) based thinfilm transistors (TFTs) are considered as the most prominent candidate for next-generation flexible display systems<sup>[1-3]</sup> and many other applications.<sup>[4]</sup> The TFT parameters of field-effect mobility ( $\mu_{FE}$ ), ON/OFF ratio, sub-threshold swing (SS), and the threshold voltage  $(V_{\text{th}})$  are critical for the practical applications. These parameters are strongly influenced by the oxygen vacancies in the active layer. The high-temperature (> 300 °C) post-annealing process is required to control the concentration of oxygen vacancies to optimize the electrical characteristics.<sup>[5-7]</sup> However, such high processing temperature is generally incompatible to many common polymer substrates. Besides, the  $\mu_{\rm FE}$  and  $V_{\rm th}$  show opposite dependence on the carrier concentration: the high carrier concentration of the active layer leads to a large  $\mu_{FE}$  but a negative and poorcontrollable  $V_{\rm th}$ , while the lower carrier concentration results in a positive  $V_{\rm th}$  but a much lower  $\mu_{\rm FE}$ .<sup>[8]</sup>

Many groups have adopted the dual-active-layer architecture (DAL) to solve this contradiction and achieve high mobility and suitable  $V_{\text{th}}$  simultaneously. The DAL normally contains of a bottom layer with high electron concentration and a top layer with low defect density. The former is close to the channel and the latter close to the contacts. Kim *et al.* reported the DAL TFT with indium–zinc oxide (IZO) or indium–tin oxide (ITO) bottom layer and InGaZnO (IGZO) top layer.<sup>[8]</sup> The thin IZO or ITO layer is for the high mobility and IGZO layer for the suitable  $V_{\text{th}}$ . Kim *et al.* proposed the solution-processed

DOI: 10.1088/1674-1056/28/8/087302

AlInZnO (AIZO)/InZnO (IZO) DAL TFTs and came to a similar conclusion.<sup>[9]</sup> Marrs *et al.* fabricated the IGZO/IZO DAL TFTs on flexible plastic substrates and demonstrated that the high saturation mobility and good gate bias stress stability could be achieved without the necessity of high-temperature annealing.<sup>[10]</sup> Many other groups studied the influence of the components of the two layers, or the thickness of the bottom layer with high carrier concentration, on the performance and stability of the devices.<sup>[11–18]</sup>

Compared with the above-mentioned hetero-DAL structures, the homo-DAL structure possesses simple fabrication process. Nag *et al.* proposed the single-source dual-layer concept and applied it to the display and circuits.<sup>[19]</sup> Tian *et al.* fabricated fully transparent DAL IGZO TFTs with different oxygen compositions in two layers.<sup>[20]</sup> Park *et al.* studied the influence of oxygen vacancy concentrations in both IGZO layers on the device stabilities.<sup>[21]</sup> In the present study, we fabricate the DAL IGZO TFTs by simply adjusting the O<sub>2</sub>/Ar gas

\*Project supported by the National Natural Science Foundation of China (Grant Nos. 11674405, 61874139, and 11675280)

<sup>†</sup>Corresponding author. E-mail: zxmei@iphy.ac.cn

<sup>‡</sup>Corresponding author. E-mail: xldu@iphy.ac.cn

<sup>© 2019</sup> Chinese Physical Society and IOP Publishing Ltd

ratio during the sputtering at 100 °C without post-annealing, and investigate the effect of the thickness of both the bottom layer (low resistance layer) and the top layer (high resistance layer) on the TFT parameters. The dependence of positive gate bias stress stabilities and hysteresis phenomena on the thickness of each layer is explored and analyzed as well. Role of the IGZO homojunction interface was revealed based on the morphology characterization of the bottom layer and its influence on the device performance.

## 2. Experiment

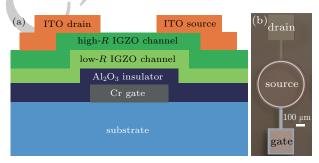

The structure of the DAL IGZO TFTs are illustrated in Fig. 1(a). First, a 35-nm-thick Cr gate layer is deposited on quartz glass by radio frequency (RF) magnetron sputtering and patterned by UV-lithography followed by wet etching (JET-929, Changsha Jinxin Electronic Materials Co. LTD). Then a 30-nm-thick Al<sub>2</sub>O<sub>3</sub> gate dielectric layer is deposited by atomic layer deposition (ALD) and patterned by UV-lithography and wet etching (hot dilute AZ 300MIF developer). The low resistance (low-R) IGZO layer is prepared by RF-magnetron sputtering at 100 °C with pure Ar atmosphere, followed by the in situ deposition of a high resistance (high-R) IGZO layer at 100 °C with a mixed sputtering gas of  $Ar/O_2 = 10:4$ . The DAL channel is patterned by the third-step UV-lithography and wet etching (dilute hydrochloric acid). Lastly, a 100nm-thick ITO source/drain electrode is deposited by RFmagnetron sputtering and patterned by a lift-off method. No post-annealing treatment was conducted on the as-fabricated TFTs.

To investigate the effect of active layer thickness on the TFT performance, we first vary the growth time of low-*R* IGZO from 0 min to 5 min while keeping a constant 30 min growth of high-*R* IGZO layer. The low-*R* IGZO was optimized as 4 min in this case, then the high-*R* IGZO was adjusted from 15 min to 60 min. The samples are labelled as (growth time of low-*R*)+(growth time of high-*R*). For instance, 3 + 30 means that the growth time of low-*R* layer is 3 min and high-*R* layer 30 min.

Fig. 1. Schematic diagram of DAL IGZO TFT. (a) Structure from the cross-section view. (b) Micrograph from the top view. The scale bar represents  $100 \ \mu m$ .

The film thickness is measured by a surface profiler (KLA-Tencor P-6). The electrical properties are revealed by

using Van der Pauw method (HMS-3000, Ecopia). The surface morphology and roughness are evaluated by atomic force microscopy (AFM, Dimension Edge, Bruker). *I–V* characteristics measurements are performed in dark using a Keithley 4200 semiconductor characterization system.

The circular Corbino TFT structure can be seen in Fig. 1(b). The inner cycle with the radius  $R_1$  of 252 µm is the source and the outer ring with the radius  $R_2$  of 268 µm the drain. The channel length (*L*) is given by  $R_2$ - $R_1$ , whereas the effective channel width (*W*) is  $\pi(R_1 + R_2)$ . The  $\mu_{\text{FE}}$  and SS are derived from the forward sweep of transfer characteristics with a drain voltage ( $V_{\text{DS}}$ ) of 0.1 V using the following equations:<sup>[3]</sup>

where  $C_{ox}$  is the specific capacitance of the gate dielectric per unit area,  $I_{DS}$  the drain current, and  $V_{GS}$  the gate voltage. The ON/OFF ratio is defined as the absolute value of the ratio of  $I_{DS}$  at  $V_{GS} = 10$  V to that at  $V_{GS} = -10$  V for comparison. The  $V_{th}$  is defined as the value of  $V_{GS}$  when  $I_{DS} = W/L * 1$  nA in the linear region. The hysteresis voltage ( $V_{H}$ ) is defined as the difference in  $V_{th}$  extracted from  $V_{GS}$  sweeps between offto-on and on-to-off. All TFT parameters except for  $V_{H}$  are obtained from three independent devices where each test is repeated three times.

#### 3. Results and discussion

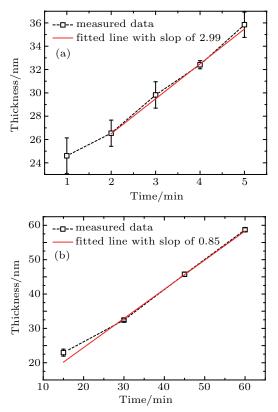

The dependence of total active layer thickness on the low-*R* IGZO growth time and high-*R* IGZO growth time is demonstrated in Fig. 2(a) and Fig. 2(b), respectively. The growth rates are extracted from the linear-fitting, which are 2.99 nm/min for low-*R* IGZO and 0.85 nm/min for high-*R* IGZO, respectively. In fact, the IGZO grows much slower under an oxygen-rich condition.<sup>[22]</sup>

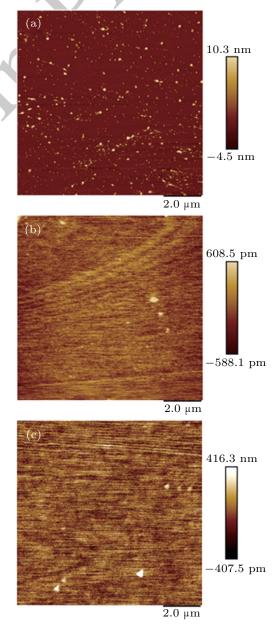

Figure 3 shows the surface morphology of low-*R* IGZO films. For the growth time of 1 min, the surface is island-like and the root mean square (RMS) roughness is 1.60 nm, as shown in Fig. 3(a). When the growth time increases to 2 min, the islands coalesce into a smooth film with a low RMS roughness of 0.304 nm [Fig. 3(b)]. Figure 3(c) indicates that the 4 min low-*R* IGZO film becomes even smoother, where the RMS roughness is 0.140 nm. The smooth surface of low-*R* IGZO facilitates the formation of abrupt homo-interface with high-*R* IGZO, which is of great importance for the electron transport.<sup>[17]</sup>

**Fig. 2.** The dependence of total channel layer thickness on the growth time of (a) the low-*R* IGZO layer (with 30 min high-*R* IGZO layer) and (b) the high-*R* IGZO layer (with 4 min low-*R* IGZO layer), respectively.

The low-*R* IGZO film sputtered under oxygen-deficient condition contains a large number of oxygen vacancies, which leads to a high electron concentration of  $1.52 \times 10^{19}$  cm<sup>-3</sup>. Such high concentration of electrons could passivate the trap states at the interface between channel and dielectric layers effectively.<sup>[14,23]</sup> The Hall mobility of low-*R* IGZO is  $10.4 \text{ cm}^2/\text{V} \cdot \text{s}$  and the resistivity  $3.97 \times 10^{-2} \Omega \cdot \text{cm}$ . The resistance of high-*R* IGZO film is higher than 200 M $\Omega$  and cannot be measured in the HMS-3000 Hall system.

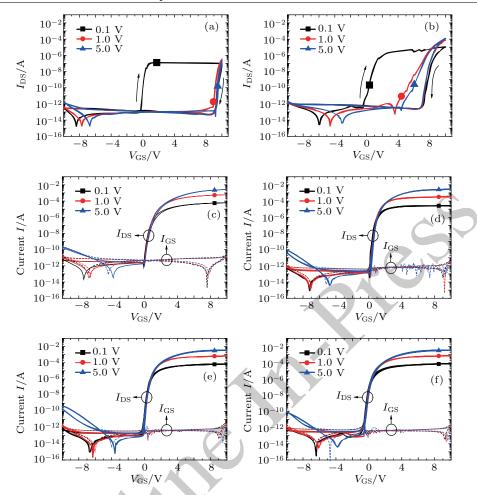

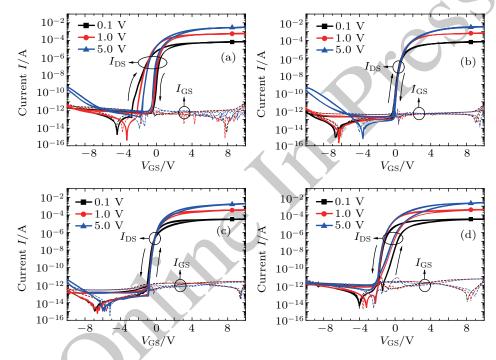

Figure 4 shows the transfer characteristics for the IGZO TFTs with different thickness of low-R layers. The TFT parameters are summarized in Table 1. The 0+30 sample, *i.e.*, the sample only containing high-R IGZO single-active layer, exhibits a very low ON/OFF ratio of about 200 and very large  $V_{\rm H}$  above 9 V at  $V_{\rm DS} = 0.1$  V, where the on-state  $I_{\rm DS}$  even decreases with elevated  $V_{GS}$ , as shown in Fig. 4(a). The transfer curve with  $V_{\rm DS} = 5$  V presents  $V_{\rm th} > 9$  V and degraded  $I_{\rm DS}$  with respect to that of  $V_{\rm DS} = 1$  V. The defects are generated at the dielectric interface during the sputtering of IGZO, which would trap the electron during the  $V_{GS}$  sweeping and lead to the low on-state  $I_{DS}$ , large clockwise  $V_{\rm H}$  and nonequilibrium, non-steady-state TFT operation.<sup>[24]</sup> The ON/OFF ratio increases by two orders of magnitude after inserting a 1 min low-R IGZO layer, but the  $V_{\rm H}$  is still very large, as shown in Fig. 4(b). AFM image in Fig. 3(a) demonstrates that the 1 min low-R IGZO is discontinuous so that the current flows partly though low-*R* IGZO and partly though high-*R* IGZO. A large number of defects remain at the interface between the dielectric and high-*R* IGZO layers, which will still trap the electrons and lead to the non-equilibrium, non-steadystate TFT operation. The 2-min low-*R* IGZO layer turns into continuous film, benefitting the passivation of the interface defects by the large number of electrons. The ON/OFF ratio is ~ 10<sup>7</sup>, even reaching 10<sup>10</sup> when the minimum and maximum currents at  $V_{DS} = 5$  V are chosen. The  $V_{H}$  is smaller than 0.3 V [Fig. 4(c)]. Note that the  $V_{th}$  shifts in the negative direction with thicker low-*R* IGZO layer due to the increasing total number of electrons [Figs. 4(c)–4(f)]. The best TFT performance belongs to the 4+30 sample, where the  $\mu_{FE}$  is  $5.41 \pm 0.05$  cm<sup>2</sup>/V·s, SS 95.0 ± 6.9 mV/dec, ON/OFF ratio  $6.70 \pm 0.95 \times 10^7$ ,  $V_{th}$ 0.24 ± 0.12 V, and  $V_{H}$  0.13 V.

**Fig. 3.** AFM image of low-*R* IGZO film with the growth time of (a)  $1 \min_{x} (b) 2 \min_{x} (a) 4 \min_{x} (b) 2 \min_{x} (b) 2 \min_{x} (b) 4 \max_{x} (b) 4 \max_{x}$

Fig. 4. Transfer characteristics for IGZO TFTs with different thickness of low-*R* layers: (a) 0+30, (b) 1+30, (c) 2+30, (d) 3+30, (e) 4+30, and (f) 5+30.

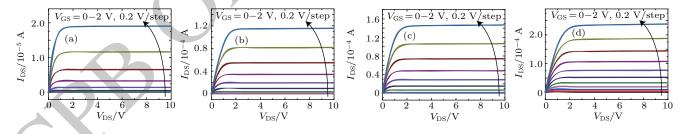

Figure 5 manifests the output characteristics of the IGZO TFTs with various thickness of low-*R* layers. The curves do not show much difference except for the current values. The excellent saturation demonstrates the small contact resistances.

Fig. 5. Output characteristics of IGZO TFTs with different thicknesses of low-R layers: (a) 2+30, (b) 3+30, (c) 4+30, and (d) 5+30.

Table 1. Summary of TFT parameters for low-R IGZO layer with different thicknesses.

| Samples | Thickness/nm     | $\mu_{\rm FE}/({\rm cm}^2/{\rm V}{\cdot}{\rm s})$ | SS/(mV/dec)    | ON/OFF ratio                  | $V_{ m th}/ m V$ | $V_{\rm H}/{ m V}$ |

|---------|------------------|---------------------------------------------------|----------------|-------------------------------|------------------|--------------------|

| 0+30    | $18.87 \pm 0.50$ | _                                                 | _              | $1.93 	imes 10^2$             | _                | > 9                |

| 1+30    | $24.60\pm1.54$   | -                                                 | _              | $7.25 	imes 10^4$             | -                | 4.87               |

| 2+30    | $26.54 \pm 1.12$ | $4.63\pm0.19$                                     | $180\pm33$     | $7.29 \pm 2.54 \times 10^{6}$ | $0.51\pm0.10$    | 0.22               |

| 3+30    | $29.82 \pm 1.13$ | $4.43 \pm 0.36$                                   | $80.2 \pm 4.2$ | $6.35\pm1.49\times10^7$       | $0.35\pm0.03$    | 0.12               |

| 4+30    | $32.41\pm0.35$   | $5.41\pm0.05$                                     | $95.0 \pm 6.9$ | $6.70 \pm 0.95 \times 10^{7}$ | $0.24\pm0.12$    | 0.13               |

| 5+30    | $35.84 \pm 1.09$ | $5.14\pm0.09$                                     | $120\pm3.5$    | $5.00\pm0.66\times10^7$       | $-0.26 \pm 0.05$ | 0.14               |

The transfer characteristics for the IGZO TFTs with various thickness of high-*R* IGZO layers are shown in Fig. 6. The 4+15 sample exhibits large clockwise hysteresis, which is reduced to smaller than 0.2 V for the 4+30 sample. Intriguingly, the hysteresis changes its direction from clockwise to counterclockwise for the 4+45 sample, and the counterclockwise hysteresis becomes bigger when the thickness of high-*R* IGZO layer further increases. The TFT parameters are summarized in Table 2. The hysteresis voltage  $V_{\rm H}$  gradually changes from 1.47 V to -1.41 V as the thickness of high-*R* IGZO increases. Generally, the counterclockwise hysteresis phenomenon is attributed to several mechanisms: (i) acceptor-like defects in dielectric or at the channel/dielectric interface,<sup>[25,26]</sup> (ii) slow polarization in the dielectric layer,<sup>[27–29]</sup> (iii) mobile charges,<sup>[30,31]</sup> (iv) charges injected from the gate electrode,<sup>[32–34]</sup> and (v) negative capacitance by ferroelectric dielectric,<sup>[35,36]</sup> but none of them can explain the transition trends with the thickness change of the high-*R* IGZO. In this case, the interface between the dielectric

tric and channel is all the same for these samples, while the only difference is the high-*R* IGZO layer. The counterclockwise hysteresis has also been reported in bilayer InGaO TFTs with 10-nm-thick front channel layer and 40-nm-thick back channel layer,<sup>[37]</sup> where the thickness of both layer are close to that of 4+60 sample. ZnO/ZnMgO field-effect transistors with two-dimensional electron gas in the ZnO channel also exhibit counterclockwise hysteresis.<sup>[38]</sup> The existence of large amount of carriers in the channel might be the origination of the hysteresis phenomenon. The mechanism needs to be further investigated.

Fig. 6. Transfer characteristics for IGZO TFTs with different thicknesses of high-*R* layers: (a) 4+15, (b) 4+30, (c) 4+45, and (d) 4+60.

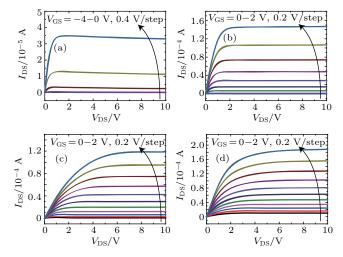

The  $\mu_{\text{FE}}$  and ON/OFF ratio significantly decrease as the growth time of high-*R* IGZO is larger than 45 min. The offstate  $I_{\text{DS}}$  at  $V_{\text{DS}} = 5$  V also decreases with the thickness of high-*R* IGZO increases. The slight degradation of saturation current in Fig. 7(a) can also be reflected from the transfer curves in Fig. 6(a), and it is different with the oversaturation hump phenomena.<sup>[20,39–41]</sup> The mechanism also needs to be further investigated. The degraded saturation current is recovered when the growth time of high-*R* IGZO increases to 30 min [Fig. 7(b)]. On the other hand, the thick high-*R* IGZO acts as a large resistor that connects in series with the channel, resulting in the reduction of  $\mu_{\text{FE}}$  and off-state  $I_{\text{DS}}$  as well as the contact resistance. The large contact resistance leads to the increase of pinch-off voltage, as shown in the output characteristics for the IGZO TFTs in Fig. 7(c) and Fig. 7(d).

The 4+30 sample presents the best TFT performance in all these samples. It is found that the thickness of low-*R* IGZO exerts little influence over the device performance as long as it forms continuous and smooth film. However, the thickness of high-*R* IGZO has a huge impact on  $\mu_{\text{FE}}$ ,  $V_{\text{th}}$ , and  $V_{\text{H}}$ . It

was reported that the thick back channel layer (high-R layer in this work) controls the charge conductance resulting in suitable threshold voltage.<sup>[9]</sup> Here, we demonstrate that this layer also has a great effect on the hysteresis.

**Fig. 7.** Output characteristics for IGZO TFTs with different thicknesses of high-*R* layers: (a) 4+15, (b) 4+30, (c) 4+45, and (d) 4+60.

| Samples | Thickness/nm     | $\mu_{FE}/(cm^2/V \cdot s)$ | SS/(mV/dec)  | ON/OFF ratio                | $V_{ m th}/ m V$ | $V_{\rm H}/{ m V}$ |

|---------|------------------|-----------------------------|--------------|-----------------------------|------------------|--------------------|

| 4+15    | $22.95 \pm 1.02$ | $4.86\pm0.30$               | $191\pm16$   | $1.82{\pm}0.17{\times}10^7$ | $-1.85\pm0.07$   | 1.47               |

| 4+30    | $32.41\pm0.35$   | $5.41\pm0.05$               | $95.0\pm6.9$ | $6.70{\pm}0.95{\times}10^7$ | $0.24\pm0.12$    | 0.13               |

| 4+45    | $45.75\pm0.61$   | $1.62\pm0.25$               | $115\pm4.3$  | $5.80{\pm}2.69{\times}10^7$ | $-0.07 \pm 0.15$ | -0.05              |

| 4 + 60  | $58.72\pm0.56$   | $1.60\pm0.14$               | $243\pm17$   | $1.73{\pm}1.47{\times}10^7$ | $0.16\pm0.03$    | -1.41              |

Table 2. Summary of TFT parameters for high-R IGZO layer with different thicknesses.

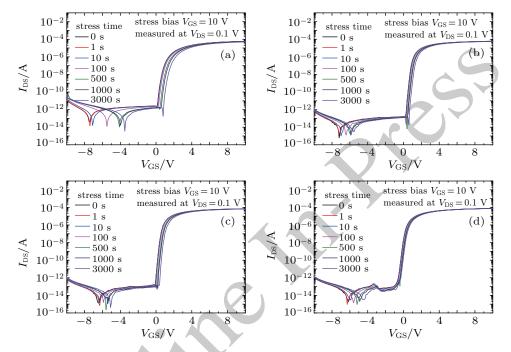

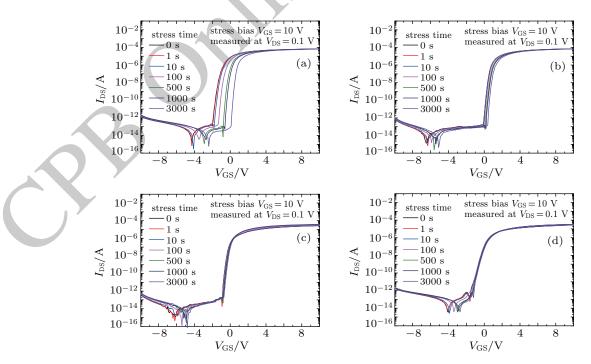

Fig. 8. Evolution of the transfer characteristics of IGZO TFTs for (a) 2+30, (b) 3+30, (c) 4+30, and (d) 5+30.

Fig. 9. Evolution of the transfer characteristics of IGZO TFTs for (a) 4+15, (b) 4+30, (c) 4+45, and (d) 4+60.

The positive gate bias stress (PBS) characteristics of the IGZO TFTs with different thicknesses of low-*R* IGZO layers are shown in Fig. 8, and Fig. 9 with different high-*R* IGZO lay-

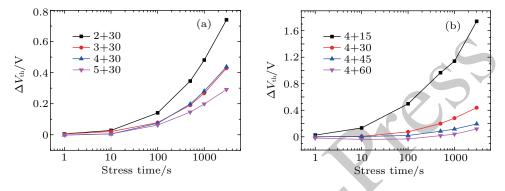

ers. The transfer characteristics were measured at  $V_{\text{DS}} = 0.1 \text{ V}$ under a gate bias stress of  $V_{\text{GS}} = 10 \text{ V}$  at set intervals. The PBS results in positive  $V_{\text{th}}$  shift ( $\Delta V_{\text{th}}$ ) for all samples. The value of SS is basically unchanged for all TFTs (not shown here). Therefore, the  $V_{\rm th}$  shifts are dominated by the charge trapping in the gate dielectric or at the channel–dielectric interface rather than defect creation.<sup>[42–44]</sup> The threshold voltage shifts *versus* stress time are shown in Fig. 10. The value of  $\Delta V_{\rm th}$  decreases with thicker low-*R* IGZO, as shown in Fig. 10(a). This can be attributed to the increase of total amount of elec-

trons, which passivate the trap states. The value of  $\Delta V_{\text{th}}$  also decreases with thicker high-*R* IGZO, as shown in Fig. 10(a). The dynamic interaction between the ambient atmosphere and the exposed back channel affects the  $V_{\text{th}}$  stability. Although there is no extra passivation layer to protect the back channel, the high-*R* IGZO layer serves as a passivation for the TFTs and inhibits the back channel formation.<sup>[5,44]</sup>

Fig. 10. The threshold voltage shifts versus stress time with different growth times of (a) low-R IGZO layer and (b) high-R layer.

## 4. Conclusion

In summary, dual-active-layer IGZO TFTs with various thickness of both layers have been fabricated, and their effects on TFT performance and stability have been investigated. When a continuous and smooth low-*R* layer forms, the  $\mu_{FE}$ , ON/OFF ratio,  $V_{th}$ , and  $V_{H}$  are significantly improved due to the passivation of defects and the high-quality homojunction interface. The influence becomes weak after the thickness of low-*R* layer is thicker than about 10 nm. The high-*R* layer not only affects the value of  $\mu_{FE}$  and  $V_{th}$ , but also has a huge impact on the  $V_{H}$ . The hysteresis gradually changes from clockwise to counterclockwise with the increasing thickness of high-*R* layer. The  $V_{th}$  shifts decreases with both thicker low-*R* and high-*R* layer. The excellent stability of DAL IGZO TFTs facilitates its applications in AMLCD and AMOLED.

## References

- [1] Kamiya T, Nomura K and Hosono H 2010 *Sci. Technol. Adv. Mater.* **11** 044305

- [2] Fortunato E, Barquinha P and Martins R 2012 Adv. Mater. 24 2945

- [3] Petti L, Münzenrieder N, Vogt C, Faber H, Büthe L, Cantarella G, Bottacchi F, Anthopoulos T D and Tröster G 2016 Appl. Phys. Rev. 3 021303

- [4] Wang K 2017 SID Symp. Dig. Tech. Pap. 48 497

- [5] Chen W T, Lo S Y, Kao S C, Zan H W, Tsai C C, Lin J H, Fang C H and Lee C C 2011 *IEEE Electron Device Lett.* 32 1552

- [6] Ye Z, Xu H, Liu T, Liu N, Wang Y, Zhang N and Liu Y 2017 IEEE Trans. Electron. Devices 64 4114

- [7] Huo W, Mei Z, Zhao M, Sui Y, Zhao B, Zhang Y, Wang T, Cui S, Liang H, Jia H and Du X 2018 *IEEE Trans. Electron. Devices* 65 3791

- [8] Kim S I, Kim C J, Park J C, Song I, Kim S W, Huaxiang Yin, Eunha Lee, Jae Chul Lee and Youngsoo Park 2008 2008 IEEE International Electron Devices Meeting 2008 IEEE International Electron Devices Meeting (IEDM) (San Francisco, CA, USA: IEEE) pp. 1–4

- [9] Kim K M, Jeong W H, Kim D L, Rim Y S, Choi Y, Ryu M K, Park K B and Kim H J 2011 IEEE Electron Dev. Lett. 32 1242

- [10] Marrs M A, Moyer C D, Bawolek E J, Cordova R J, Trujillo J, Raupp G B and Vogt B D 2011 *IEEE Trans. Electron. Dev.* 58 3428

- [11] Jeong W H, Kim K M, Kim D L, Rim Y S and Kim H J 2012 IEEE Trans. Electron. Dev. 59 2149

- [12] Seo J S and Bae B S 2014 ACS Appl. Mater. Interfaces 6 15335

- [13] Lee S H and Choi W S 2015 J. Disp. Technol. 11 698

- [14] Abliz A, Huang C W, Wang J, Xu L, Liao L, Xiao X, Wu W W, Fan Z, Jiang C, Li J, Guo S, Liu C and Guo T 2016 ACS Appl. Mater. Interfaces 8 7862

- [15] Choi J H, Yang J, Nam S, Pi J, Kim H, Kwon O, Park E, Hwang C and Cho S H 2016 IEEE Electron Dev. Lett. 37 1295

- [16] Liu Y R, Zhao G W, Lai P T and Yao R H 2016 *Chin. Phys. B* 25 088503

- [17] Faber H, Das S, Lin Y H, Pliatsikas N, Zhao K, Kehagias T, Dimitrakopulos G, Amassian A, Patsalas P A and Anthopoulos T D 2017 *Sci. Adv.* 3 e1602640

- [18] Stewart K A, Gouliouk V, McGlone J M and Wager J F 2017 IEEE Trans. Electron. Dev. 64 4131

- [19] Nag M, Chasin A, Rockele M, Steudel S, Myny K, Bhoolokam A, Tripathi A, van der Putten B, Kumar A, van der Steen J L, Genoe J, Li F, Maas J, van Veenendaal E, Gelinck G and Heremans P 2013 J. Soc. Inf. Disp. 21 129

- [20] Tian Y, Han D, Zhang S, Huang F, Shan D, Cong Y, Cai J, Wang L, Zhang S, Zhang X and Wang Y 2014 Jpn. J. Appl. Phys. 53 04EF07

- [21] Park J H, Kim Y, Yoon S, Hong S and Kim H J 2014 ACS Appl. Mater. Interfaces 6 21363

- [22] Yang D G, Do Kim H, Kim J H, Lee S W, Park J, Kim Y J and Kim H S 2017 Thin Solid Films 638 361

- [23] Xu H, Xu M, Chen Z, Li M, Zou J, Tao H, Wang L and Peng J 2016 IEEE Electron Dev. Lett. 37 57

- [24] Wager J F 2010 J. Soc. Inf. Disp. 18 749

- [25] Qian L X and Lai P T 2014 IEEE Trans. Device Mater. Reliab. 14 177

- [26] Yue L, Meng F and Chen J 2018 Semicond. Sci. Technol. 33 015012

- [27] Yang W, Song K, Jung Y, Jeong S and Moon J 2013 J. Mater. Chem. C 1 4275

- [28] Banger K, Warwick C, Lang J, Broch K, Halpert J E, Socratous J, Brown A, Leedham T and Sirringhaus H 2016 Chem. Sci. 7 6337

- [29] Ye Z, Yuan Y, Xu H, Liu Y, Luo J and Wong M 2017 IEEE Trans. Electron. Dev. 64 438

- [30] Liu Y, Guan P, Zhang B, Falk M L and Katz H E 2013 Chem. Mater. 25 3788

- [31] Jo J W, Kim K H, Kim J, Ban S G, Kim Y H and Park S K 2018 ACS Appl. Mater. Interfaces 10 2679

- [32] Lee C A, Park D W, Jin S H, Park I H, Lee J D and Park B G 2006 *Appl. Phys. Lett.* 88 252102

- [33] Daunis T B, Tran J M H and Hsu J W P 2018 ACS Appl. Mater. Interfaces 10 39435

- [34] Wang X, Gao Y, Liu Z, Luo J and Wan Q 2019 IEEE Electron Dev. Lett. 40 224

- [35] Petti L, Münzenrieder N, Salvatore G A, Zysset C, Kinkeldei T, Büthe L and Tröster G 2014 IEEE Trans. Electron. Dev. 61 1085

- [36] Li Y, Liang R, Wang J, Jiang C, Xiong B, Liu H, Wang Z, Wang X, Pang Y, Tian H, Yang Y and Ren T 2019 *IEEE Electron Dev. Lett.* 40 826

- [37] Yang C P, Chang S J, Chang T H, Wei C Y, Juan Y M, Chiu C J and Weng W Y 2017 IEEE Electron Dev. Lett. 38 572

- [38] Sasa S, Ozaki M, Koike K, Yano M and Inoue M 2006 Appl. Phys. Lett. 89 053502

- [39] Oh M S, Lee K, Song J H, Lee B H, Sung M M, Hwang D K and Im S 2008 J. Electrochem. Soc. 155 H1009

- [40] Han D, Zhang S, Zhao F, Dong J, Cong Y, Zhang S, Zhang X and Wang Y 2015 Thin Solid Films 594 Part B 266

- [41] Jian L Y, Lee H Y, Lin Y H and Lee C T 2018 J. Electron. Mater. 47 1467

- [42] Cross R B M and De Souza M M 2006 Appl. Phys. Lett. 89 263513

- [43] Suresh A and Muth J F 2008 Appl. Phys. Lett. 92 033502

- [44] Jeong J K, Won Yang H, Jeong J H, Mo Y G and Kim H D 2008 Appl. Phys. Lett. 93 123508